Hexagon DSP Processor

高通技术开发的Hexagon DSP作为一个世界级的处理器,包含CPU和DSP,其功能支持移动平台为多媒体和调制解调器而引入的深度嵌入处理需求。它是先进的、可变指令长度、超长指令字(VLIW)、基于硬件多线程的处理器架构。Hexagon架构和系列内核提供高通技术针对调制解调器和多媒体方面在性能和功耗方面的竞争优势,同时也是高通骁龙处理器的关键组成部分。

Hexagon DSP处理器背景:

高通技术是在2004年的秋季开始开发新的DSP处理器架构和高性能实现。在2011年,Hexagon Access程序开始允许客户编程DSP,通过转移ARM核心性能上的负载获取电量和性能优势,减少功耗和并发性需求。截止到2012年,高通技术使用多Hexagon核心在每一个虚拟商业运行4G LTE调制解调器后形成处理引擎。Hexagon DSP核心现在处于其第五代系列中,其集成了当前高通所有调制解调器和应用芯片技术。2013年在Uplinq,我们发布了第一个公开的、可用的Hexagon DSP开发环境,Hexagon SDK。

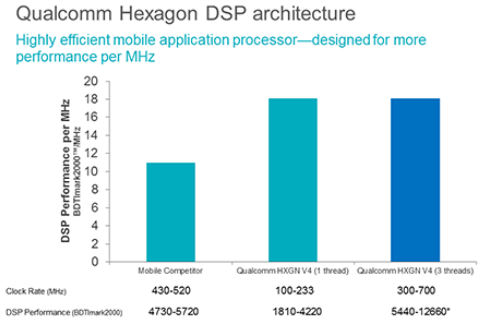

Hexagon核心为高性能和能源的效率进行了优化。能源的效率往往是更重要的指标。不是通过MHz推动性能,设计上力求每个周期工作在更高的水平,且运行在较低的时钟速度上。保持低速度的目标是允许这种实现避免很多功耗代价高昂的典型的高速度设计方法。多线程的一个挑战是正在运行的线程的数目和功耗的比率。通过精心设计分层时钟门控,近乎完美地获取功耗比例。

Very Long Instruction Word (VLIW) processor architecture

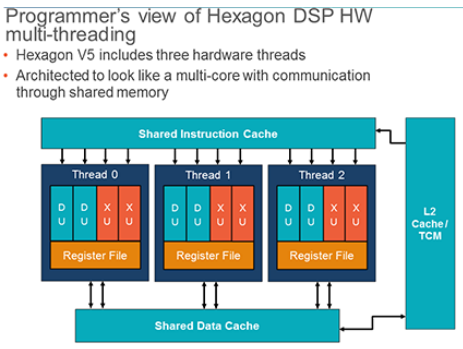

所有版本的Hexagon DSP核心都是采用硬件多线程来达到移动应用所需要的高 并发性。实现方式已经从简单的交错多线程(IMT)发展到更高级的优先级调度,以获取最大效率来安排尽可能多的执行插槽。硬件线程的数量已经修改了几个系列,以满足各种产品和应用需求。最初的HexagonV1内核支持6线程,但是最近的Hexagon DSP版本,Hexagon V5具有三个线程。对程序员来说,这些硬件线程可以当作带有共享内存的分离处理器内核,且可以用常规的软件线程来编程。

自从RTOS映射用户软件线程到处理器的硬件线程上之后,程序员就不需要在关注线程。这些硬件线程共享包括L1在内的整个存储器层级。因此,它非常有利于软件使用在共享数据上协作的线程。为了推动这项工作,一个非常快的RTOS内核已经为Hexagon设计出来。RTOS全局调度优先级最高的运行态软件线程且始终指示中断到最低优先级的硬件线程。不同于大多数架构,Hexagon指令集的 起始和演变都假设存在一个多线程实现。多线程引入的固有延迟容忍使ISA优化将变的不切合实际。Hexagon超越了传统的VLIW和允许独立的和相关形式的指令进行分组。作为一个例子,命令load-compare-branch可以表达为一个单Hexagon指令包。这种技术能够提取高并行指令,甚至来自于不规则控制代码的应用程序。

Hexagon DSP multi-threading diagram

ISA是指令的VLIW风格静态分组。多线程和VLIW是互补的技术。多线程隐藏管道延迟使指令延迟变低。低指令延迟可以使编译器更有效地利用VLIW包。Hexagon ISA混合了DSP/CPU,其特点是4-issue VLIW,包含双加载/存储插槽和双64位的向量执行插槽。所有的指令在一个共享的32项线程寄存器文件中执行。向量操作使用来自通用寄存器文件的寄存器对。ISA拥有丰富的DSP算法支持,包括16位和32位小数和复杂数据类型、32位浮点以及完整的64位整数运算。来自比如H.264、AMR-WB和AAC+等应用的有竞争的数据将被展示。

此架构的公开说明最近发表于2013年8月斯坦福大学的Hot Chips会议上。 此处理器已经被伯克利设计技术公司(BDTI)当作相关DSP处理器的标准,其是分析数字信号处理器方面领先的独立公司。

Hexagon DSP performance

BDTI公司网站上找到的基准测试结果

Hexagon处理器是硬件多线程、可变指令长度、为高效的控制性和移动设备所上低功耗信号处理代码所开发的VLIW处理器架构。

Qualcomm 开发者专区是 Qualcomm 联合CSDN 共同打造的面向中国开发者的技术专区。致力于通过提供全球最新资讯和最多元的技术资源及支持,为开发者们打造全面一流的开发环境。本专区将以嵌入式、物联网、游戏开发、Qualcomm® 骁龙™处理器的软件优化等技术为核心,打造全面的开发者技术服务社区,为下一代高性能体验和设计带来更多的想法和灵感。

加入 Qualcomm 开发者专区

申请成为“Qualcomm荣誉技术大使”

“Qualcomm荣誉技术大使”是Qualcomm开发者社区对开发者用户技术能力与影响力的认证体现,该荣誉代表Qualcomm社区对用户贡献的认可与肯定。

立即申请招贤纳士

Qualcomm在中国的业务发展迅速,每年提供大量的技术岗位,分布在北京,上海,深圳等地。Qualcomm开发者社区是开发者藏龙卧虎之地,Qualcomm中国HR特别设立了招聘通道,欢迎开发者同学踊跃报名。

Qualcomm 活动 更多

6月19日

线上